DDR4 SDRAM이 전원 인가 후 동작 상태에 도달하기까지 필요한 초기화, ZQ 캘리브레이션, VrefDQ 캘리브레이션, 읽기/쓰기 트레이닝(메모리 트레이닝) 절차를 단계별로 설명한다.

SVIO 최신 글 -- LPDDR5 튜토리얼: 물리적 구조 심층 분석

DDR4 SDRAM - 초기화, 트레이닝 및 캘리브레이션

검색 초기화

* [타이밍 파라미터](https://www.systemverilog.io/design/understanding-ddr4-timing-parameters/)

* [타이밍 파라미터 치트시트](https://www.systemverilog.io/design/ddr4-timing-parameters-cheatsheet/)

* - [x] 시스템 설계 시스템 설계

* [Open Compute Project에서의 모듈형 설계](https://www.systemverilog.io/design/modular-design-in-open-compute-project/)

* [Facebook & OCP](https://www.systemverilog.io/design/facebook-and-the-open-compute-project/)

* [HP Moonshot 설계 분석](https://www.systemverilog.io/design/hp-moonshot-dissection/)

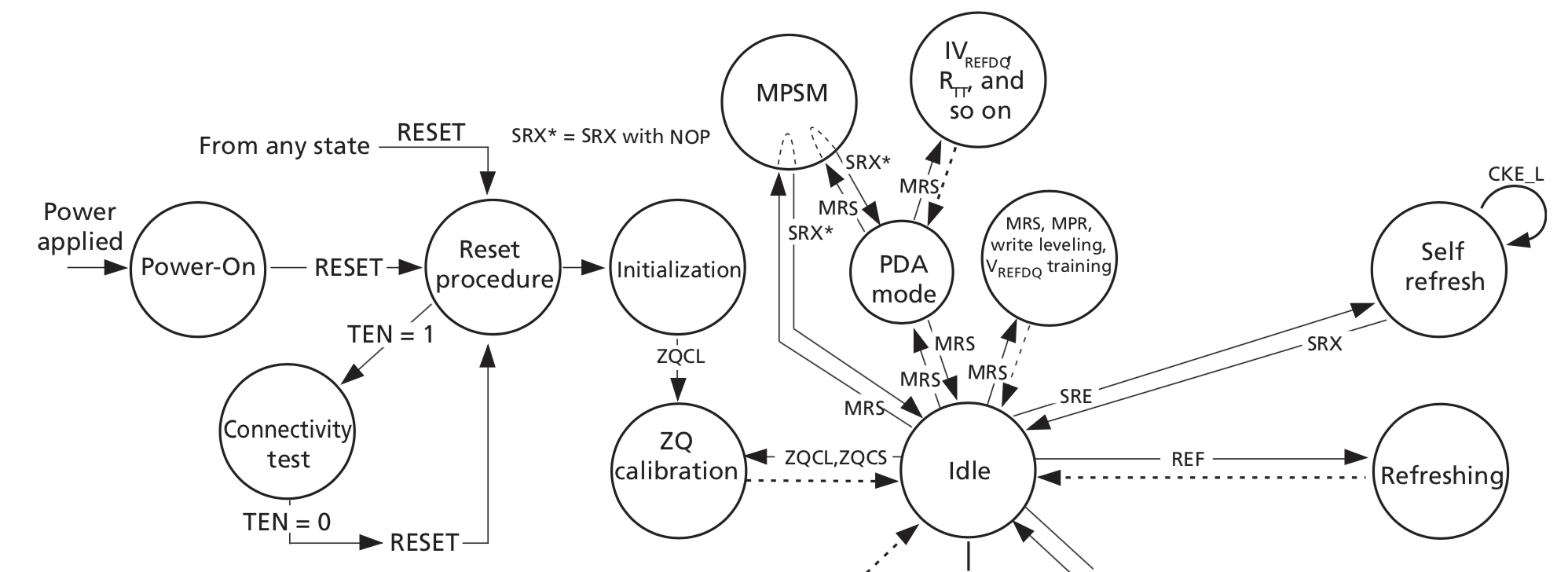

DRAM 서브시스템을 가진 디바이스에 전원이 인가되면, DRAM이 동작 가능한 상태에 도달하기 전까지 여러 가지 일이 일어납니다. 아래는 JEDEC 규격에 있는 상태 머신으로, 전원 인가 이후 DRAM이 거쳐 가는 다양한 상태 전이를 보여줍니다.

그림 1: DDR4 상태 머신 (출처: Micron 데이터시트)

요컨대, 초기화 절차는 다음의 4가지 구분되는 단계로 구성됩니다.

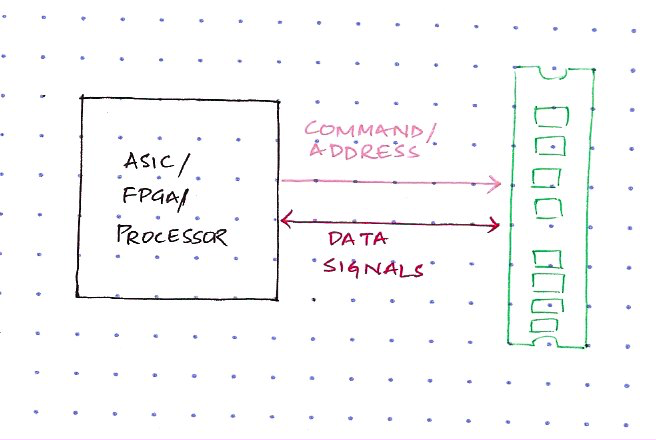

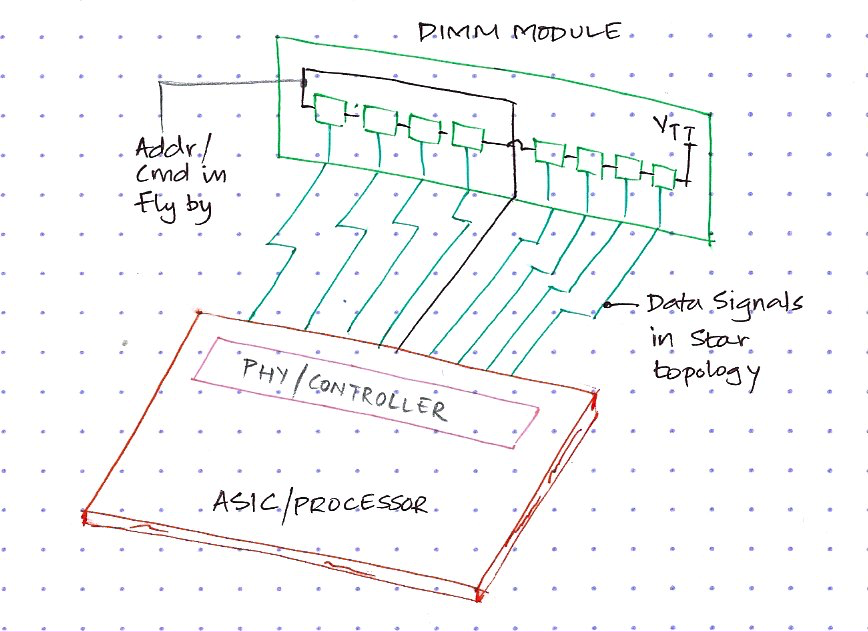

다음 섹션들을 더 잘 이해하기 위해, 아래와 같은 시스템을 가정해 봅시다. 1개의 DIMM 모듈을 가진 ASIC/FPGA/Processor입니다.

그림 2: 예시 시스템

그림 2: 초기화 상태 (출처: Micron 데이터시트)

전원 인가 및 초기화는 고정되어 있고 잘 정의된 단계들의 시퀀스입니다. 일반적으로 시스템에 전원이 인가되고 ASIC/FPGA/Processor 내부의 컨트롤러가 리셋에서 해제되면, 컨트롤러가 전원 인가 및 초기화 시퀀스를 자동으로 수행합니다. 아래는 컨트롤러가 하는 일을 아주 단순화한 버전입니다. 정확한 세부 사항은 JESD79-49A 규격의 3.3절을 참조하세요.

RESET 디어서트 및 ClockEnable CKE 활성화CK_t/CK_c 활성화MRS 명령을 발행하고 모드 레지스터 로드 [모드 레지스터는 특정 시퀀스로 로드됨]ZQCL]IDLE 상태로 전환이 시점에서 DIMM 모듈의 DRAM들은 자신들이 어떤 주파수로 동작해야 하는지, CAS Latency (CL), CAS Write Latency (CWL) 및 몇 가지 다른 타이밍 파라미터가 무엇인지 이해하고 있습니다.

Tip

CL, CWL 등의 항목을 더 알아보려면 DDR4 타이밍 파라미터 글을 확인해 보세요 ...

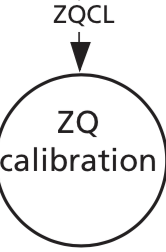

그림 4: ZQCL (출처: Micron 데이터시트)

ZQ 캘리브레이션은 데이터 핀 DQ와 관련이 있습니다. ZQ 캘리브레이션이 무엇을 하는지, 그리고 왜 필요한지 이해하려면 먼저 각 DQ 핀 뒤에 있는 회로를 봐야 합니다. DQ 핀은 양방향이라는 점을 기억하세요. 읽기 시에는 데이터를 되돌려 보내고, 쓰기 시에는 데이터를 수신하는 역할을 합니다.

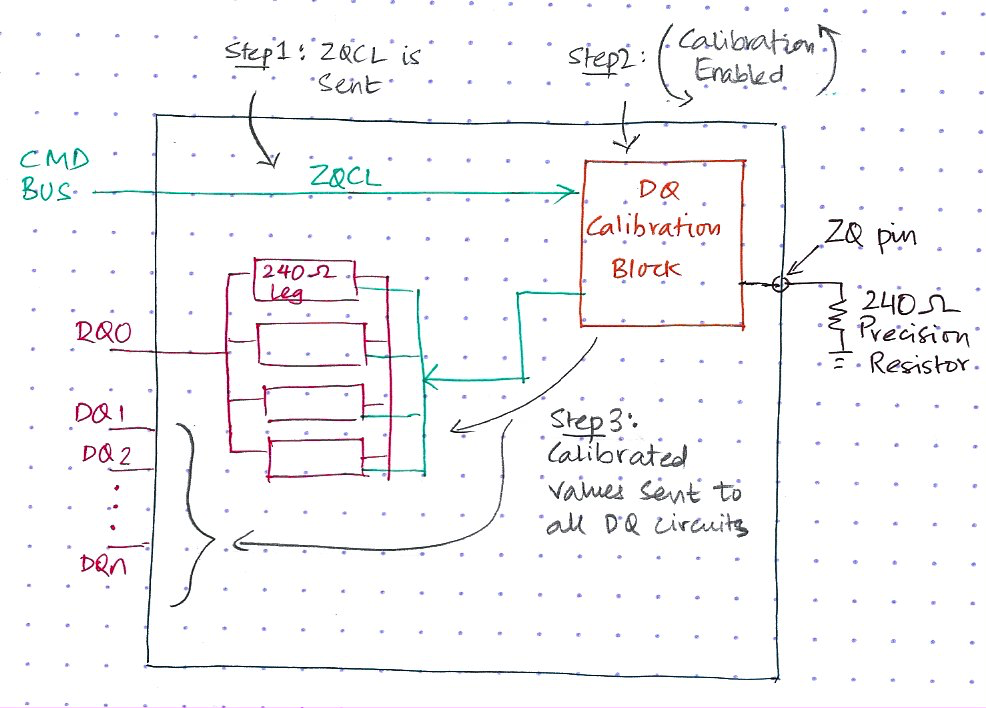

그림 5: DQ 캘리브레이션 블록

이제 DRAM 내부를 보면, 각 DQ 핀 뒤의 회로는 그림 4에 보인 것처럼 병렬 240Ω 저항 레그들의 집합으로 구성되어 있습니다. CMOS 디바이스의 특성상 이 저항들은 정확히 240Ω가 아닙니다. 저항값은 전압과 온도 변화에도 영향을 받습니다. 그래서 이들은 조정 가능하도록(tunable) 만들어집니다.

이 저항들을 정확히 240Ω로 튜닝하기 위해, 각 DRAM에는 다음이 있습니다.

정밀 (+/- 1%) 240Ω 저항이 연결되는 ZQ 핀이 외부 정밀 저항은 "기준(reference)" 이며, 모든 온도에서 240Ω를 유지합니다. 초기화 중 ZQCL 명령이 발행되면 DQ 캘리브레이션 컨트롤 블록이 활성화되고 튜닝 값을 생성합니다. 이 값은 각 DQ의 내부 회로로 복사됩니다.

Note!

위 설명은 ZQ 캘리브레이션의 빠른 개요입니다. 이 정도로 충분하다면 다음 섹션으로 넘어가세요. 더 자세한 내용이 궁금하다면 계속 읽으세요.

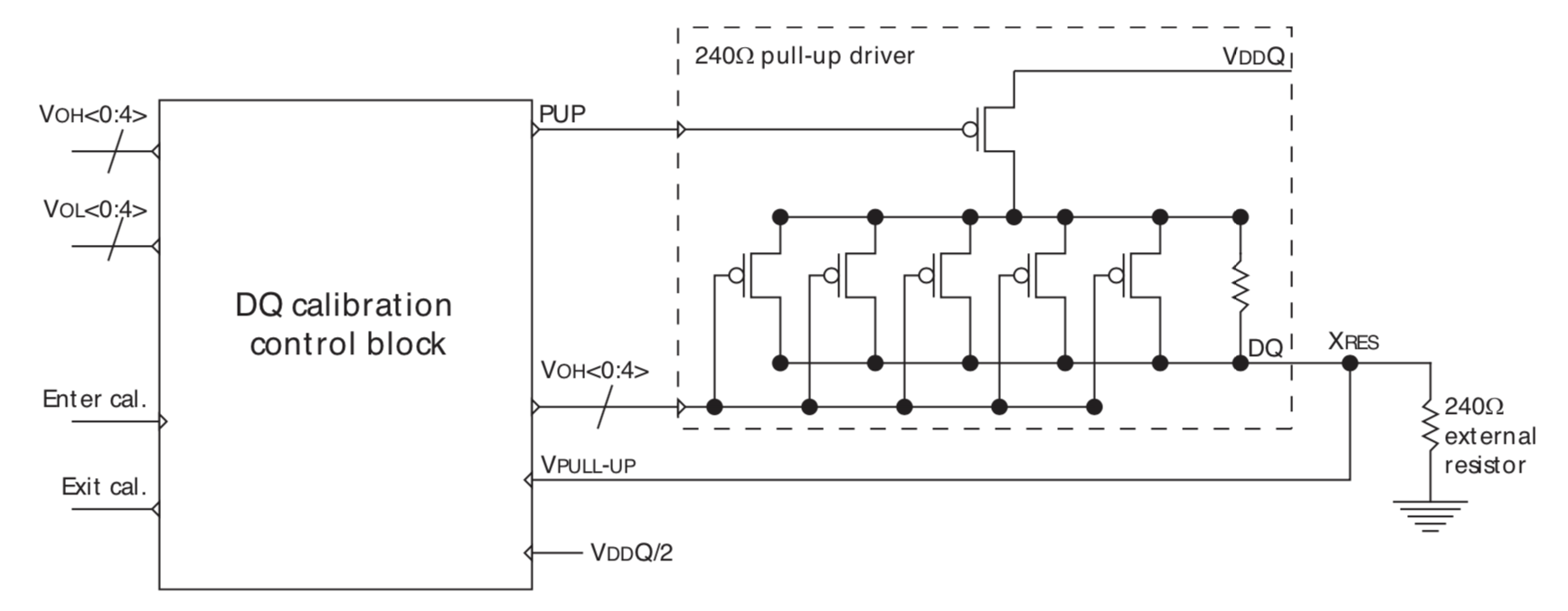

DQ 회로 내부의 240Ω 저항 레그는 "폴리 실리콘 저항(Poly Silicon Resistor)"이라는 유형의 저항이며, 일반적으로 240Ω보다 약간 큽니다(폴리 실리콘 저항은 CMOS 기술과 호환되는 저항의 한 형태입니다). 이 폴리 저항에 병렬로 연결된 다수의 p-채널 디바이스가 있어서, 이를 통해 정확히 240Ω로 튜닝할 수 있습니다.

아래 그림은 DQ 회로의 240Ω 레그 하나를 확대하여, 폴리 저항에 연결된 5개의 p-채널 디바이스를 보여줍니다. 이 작은 트랜지스터들은 입력 VOH[0:4]에 의해 설정됩니다.

그림 6: DQ 드라이버/리시버 회로 (출처: Micron 데이터시트)

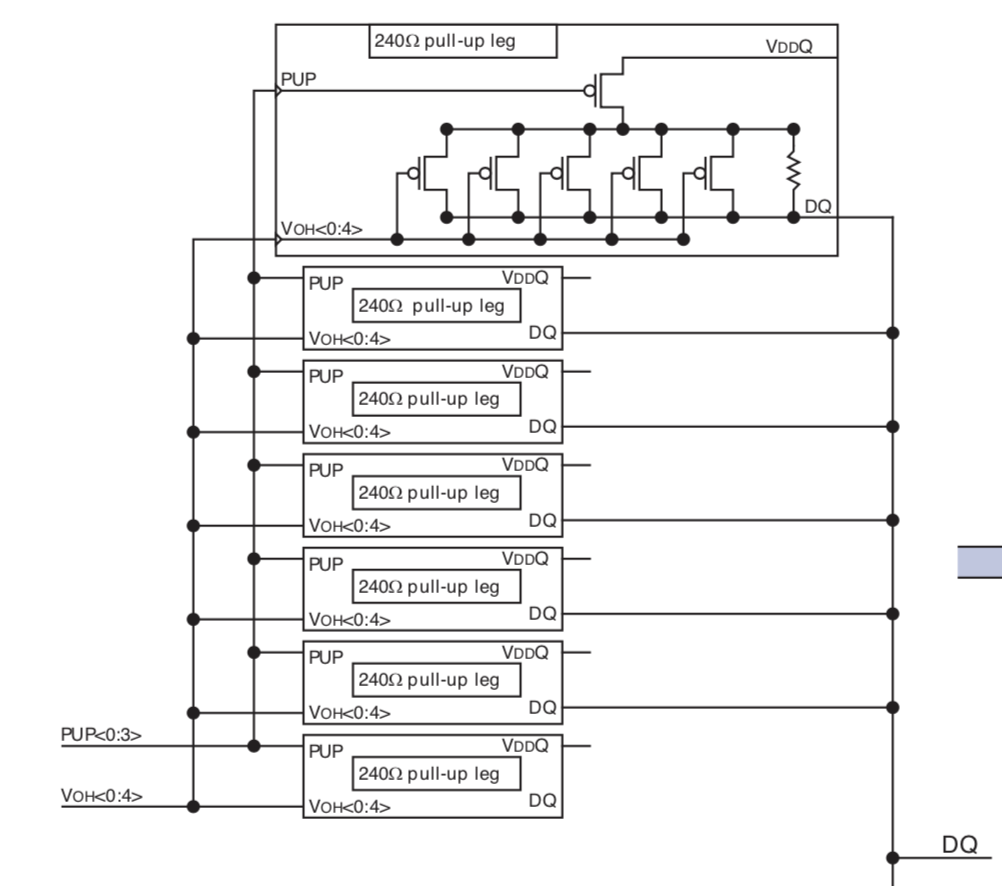

이제 DQ 캘리브레이션 컨트롤 블록에 연결된 회로는, 한 저항이 폴리 저항이고 다른 저항이 정밀 240Ω인 저항 분배기 회로입니다. 초기화 중 ZQCL 명령이 발행되면 DQ 캘리브레이션 컨트롤 블록이 활성화되고, 그 안의 내부 비교기가 VOH[0:4]를 사용해 p-채널 디바이스를 튜닝하여 전압이 정확히 VDDq/2가 될 때까지 조정합니다(전형적인 저항 분배기). 이 시점에서 캘리브레이션이 완료되며 VOH 값들이 모든 DQ 핀으로 전송됩니다.

그림 7: DQ 캘리브레이션 블록 (출처: Micron 데이터시트)

다음으로, 어째서 DQ 핀에 애초에 이런 240Ω 병렬 저항 네트워크가 필요한지 궁금할 수도 있습니다!

병렬 240Ω 저항 뱅크를 두면 구동 강도(READ 시)와 종단 저항(WRITE 시)을 튜닝할 수 있습니다. 모든 PCB 레이아웃은 서로 다르므로, 신호 무결성을 개선하고 신호 아이 크기(eye-size)를 최대화하며 DRAM이 고속에서 동작할 수 있게 하려면 이런 튜닝 기능이 필요합니다.

DRAM에서의 신호 구동 강도는 모드 레지스터 MR1[2:1] 설정으로 제어할 수 있습니다. 종단은 모드 레지스터 MR1, 2 & 5에서 각각 RTT_NOM, RTT_WR&RTT_PARK 조합으로 제어할 수 있습니다.

새 글이 발행되면 알림을 받으세요!

그림 8: VrefDQ 캘리브레이션 (출처: Micron 데이터시트)

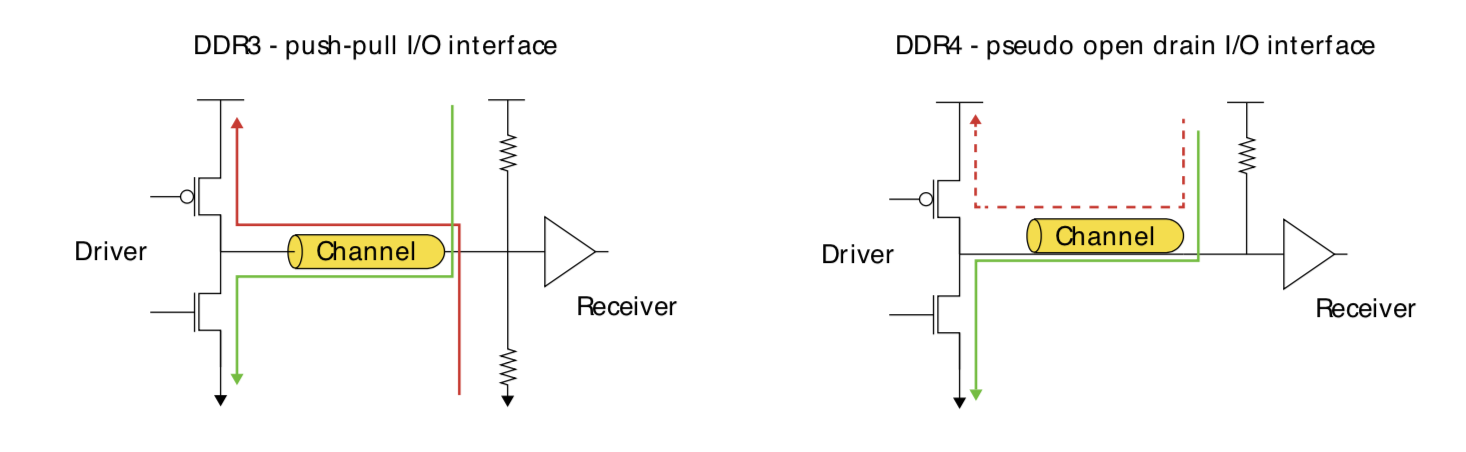

DDR4에서는 데이터 라인(DQ)의 종단 방식이 CTT(Center Tapped Termination, SSTL Series-Stud Terminated Logic라고도 함)에서 POD(Pseudo Open Drain)로 변경되었습니다. 이는 고속에서의 신호 무결성을 개선하고 IO 전력을 절감하기 위해서입니다. 이런 방식은 DDR4가 처음이 아니며, GDDR5(그래픽 DRAM)도 POD를 사용합니다.

그림 9: DDR3의 SSTL vs DDR4의 POD (출처: Micron 핸드북)

이는 DDR3에서는 Vdd/2가 DQ 신호가 0인지 1인지 결정하는 전압 기준으로 사용된다는 뜻입니다. 그림 9의 왼쪽을 다시 보면, 수신기는 본질적으로 저항 분배기 회로입니다.

하지만 DDR4에서는 수신기에 저항 분배기 회로가 없습니다. 대신 내부 전압 기준을 사용해 데이터 라인(DQ)의 신호가 0인지 1인지 결정합니다. 이 전압 기준을 VrefDQ라고 합니다. VrefDQ는 모드 레지스터 MR6로 설정할 수 있으며, VrefDQ 캘리브레이션 단계에서 메모리 컨트롤러가 이를 올바르게 설정해야 합니다.

이 시점에서 초기화 절차는 완료되었고 DRAM들은 IDLE 상태에 있지만, 메모리는 여전히 동작 가능한 상태가 아닙니다. 컨트롤러와 PHY가 DRAM에 데이터를 신뢰성 있게 쓰거나 읽기 전에 몇 가지 중요한 단계를 추가로 수행해야 합니다. 이 중요한 단계를 읽기/쓰기 트레이닝(Read/Write Training, 또는 Memory Training, 또는 Initial Calibration)이라고 하며, 이 과정에서 컨트롤러(또는 PHY)는 다음을 수행합니다.

이 섹션은 상태 머신에서 다음 원으로 표시된 부분에 대한 내용입니다.

그림 10: 읽기/쓰기 트레이닝 상태 (출처: Micron 핸드북)

예시 시스템을 더 자세히 살펴봅시다. 아래 그림은 데이터 신호와 주소/커맨드 신호가 ASIC/Soc/Processor와 DIMM 위 DRAM들 사이에 어떻게 연결되는지를 보여줍니다.

DQ & DQS)는 각 메모리가 72개의 데이터 라인 중 서로 다른 부분에 연결되기 때문에, 각 메모리로 스타 토폴로지로 연결됩니다.A, CK, CKE, WE, CSn)은 플라이-바이 라우팅(fly-by routing) 토폴로지라는 기법으로 연결됩니다. 이는 DIMM 위의 모든 DRAM이 동일한 주소 라인을 공유하며, 더 나은 신호 무결성과 고속을 달성하기 위해 플라이-바이 라우팅이 필요하기 때문입니다.

그림 11: 상세 예시 시스템

따라서 ASIC/Processor 관점에서는 DIMM 위 각 DRAM 메모리가 서로 다른 거리에 위치합니다. 혹은 DIMM 관점에서는 DIMM 위 각 DRAM마다 클록과 데이터 사이의 스큐(skew)가 다릅니다.

DRAM은 꽤 "멍청한" 디바이스입니다. 예를 들어 WRITE 동작을 하려면, 초기화 시 모드 레지스터 중 하나를 프로그래밍하여 CAS Write Latency가 무엇인지 DRAM에 알려줍니다(CWL은 컬럼 주소와 DRAM 입력에서의 데이터 사이의 시간 지연입니다). 그리고 이 타이밍 파라미터는 항상 준수해야 합니다. 메모리 컨트롤러는 보드 트레이스 지연과 플라이-바이 라우팅 지연을 고려하여 주소와 데이터를 올바른 스큐로 내보내, 주소와 데이터가 메모리에 도착했을 때 그 사이가 CWL 지연이 되도록 해야 합니다.

예를 들어 CAS Write Latency를 9로 설정했다면, ASIC/uP가 컬럼 주소를 내보낸 뒤 각 데이터 비트가 서로 다른 시점에 발사되어, 모든 데이터 비트가 DRAM에 CWL이 9가 되도록 도착해야 합니다.

READ도 비슷한 방식으로 처리해야 합니다. DIMM 위 각 DRAM은 서로 다른 거리에 있으므로 READ가 발행되면 DIMM 위 각 DRAM은 READ 커맨드를 서로 다른 시점에 보게 되고, 그 결과 각 DRAM에서 오는 데이터가 ASIC/Processor에 서로 다른 시점에 도착합니다. Initial Calibration 동안 ASIC/Processor는 각 DRAM에서의 지연이 얼마인지 파악하고, 내부 회로를 이에 맞게 트레이닝하여 여러 DRAM에서 오는 데이터를 적절한 순간에 래치(latch)하도록 합니다.

읽기/쓰기 트레이닝을 위해 컨트롤러/PHY IP는 보통 여러 알고리즘을 제공합니다. 가장 흔한 것들은 다음과 같습니다.

Write LevelingMPR (Multi-Purpose Register) Pattern WriteRead CenteringWrite Centering다음 섹션에서는 각 알고리즘을 더 자세히 설명합니다.

DRAM에 데이터를 쓸 때 위반하면 안 되는 중요한 타이밍 파라미터가 tDQSS입니다. tDQSS는 클록(CK) 대비 데이터 스트로브(DQS)의 위치입니다. tDQSS는 규격에 정의된 tDQSS(MIN)과 tDQSS(MAX) 범위 내에 있어야 합니다. tDQSS를 위반해 범위를 벗어나면 잘못된 데이터가 메모리에 써질 수 있습니다.

DIMM 위 각 DRAM마다 Clock과 Data/DataStrobe 사이의 스큐가 다르므로, 메모리 컨트롤러는 이 스큐를 보상하고 DIMM의 각 DRAM 입력에서 tDQSS를 유지할 수 있도록 자신을 트레이닝해야 합니다.

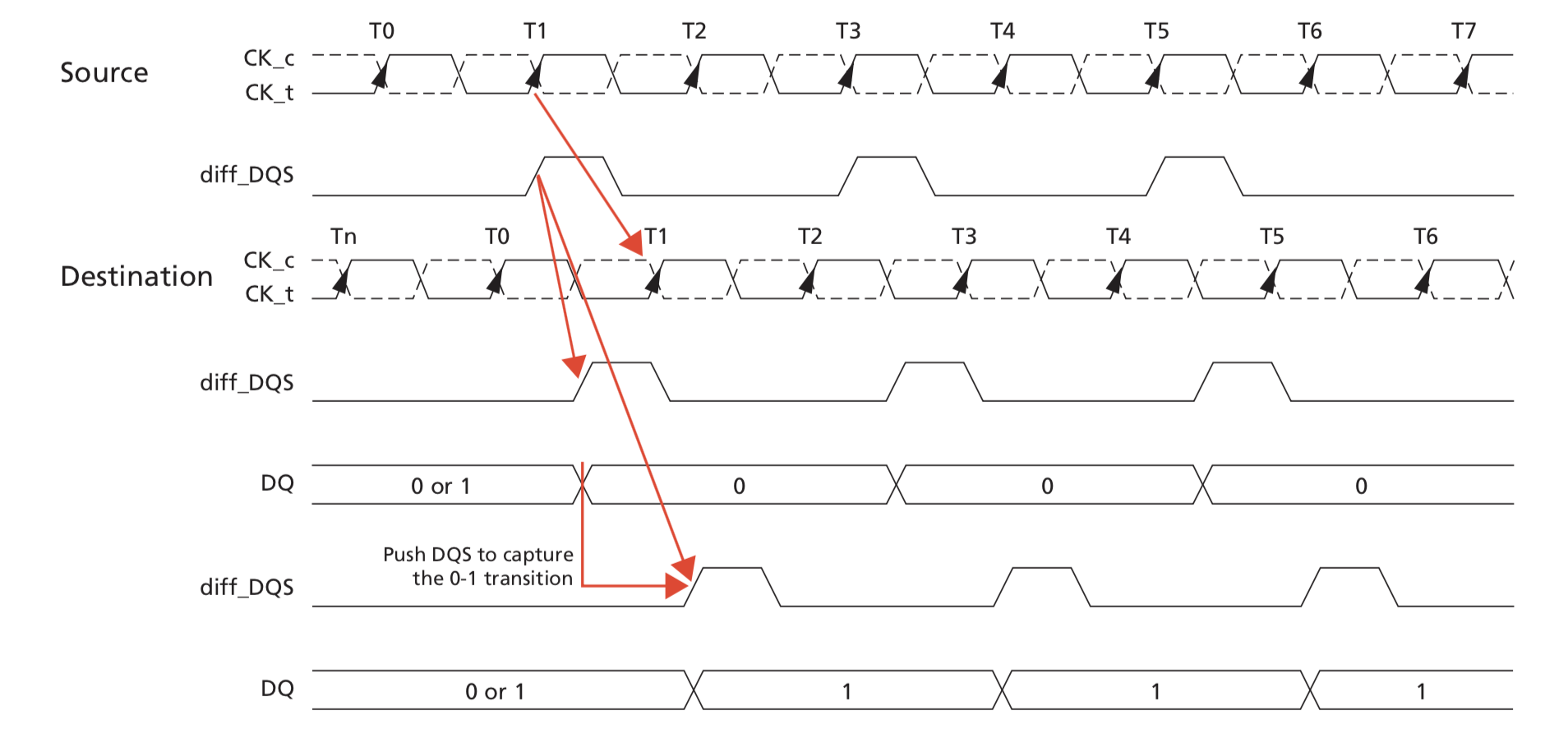

컨트롤러에서 write-leveling을 활성화하면 다음 단계를 수행합니다.

MR1에 대한 모드 레지스터 쓰기를 수행해 bit 7을 1로 설정합니다. 이는 DRAM을 write-leveling 모드로 전환합니다. write-leveling 모드에서 DRAM은 DataStrobe(DQS)를 보면 이를 사용해 클록(CK)을 샘플링하고, 샘플링된 값을 DQ 버스를 통해 컨트롤러로 되돌려 보냅니다.

컨트롤러는 DQS 펄스의 연속을 보냅니다. DRAM은 write-leveling 모드이므로 DQS로 CK 값을 샘플링하고, 이 샘플링 값(1 또는 0)을 DQ 버스로 컨트롤러에 반환합니다.

컨트롤러는 다음을 수행합니다. * DRAM이 반환한 DQ 비트 값을 확인하고 * DQS 지연을 증가시키거나 감소시키며 * 일정 시간이 지난 후 다음 DQS 펄스들을 발사합니다.

DRAM은 다시 CK를 샘플링하고 샘플 값을 DQ 버스로 반환합니다.

컨트롤러가 0에서 1로의 전이(0-to-1 transition)를 볼 때까지 2~4 단계를 반복합니다. 이 시점에서 컨트롤러는 DQS 지연 설정을 고정(lock)하며, 해당 DRAM 디바이스에 대한 write-leveling이 달성됩니다.

DIMM 전체에 대한 write-leveling 절차를 완료하기 위해, 각 DQS에 대해 2~5 단계를 반복합니다.

마지막으로 MR1[7]에 0을 써서 DRAM들을 write-leveling 모드에서 해제합니다.

아래 그림은 write-leveling 개념을 보여줍니다.

그림 12: Write Leveling (출처: Micron 데이터시트)

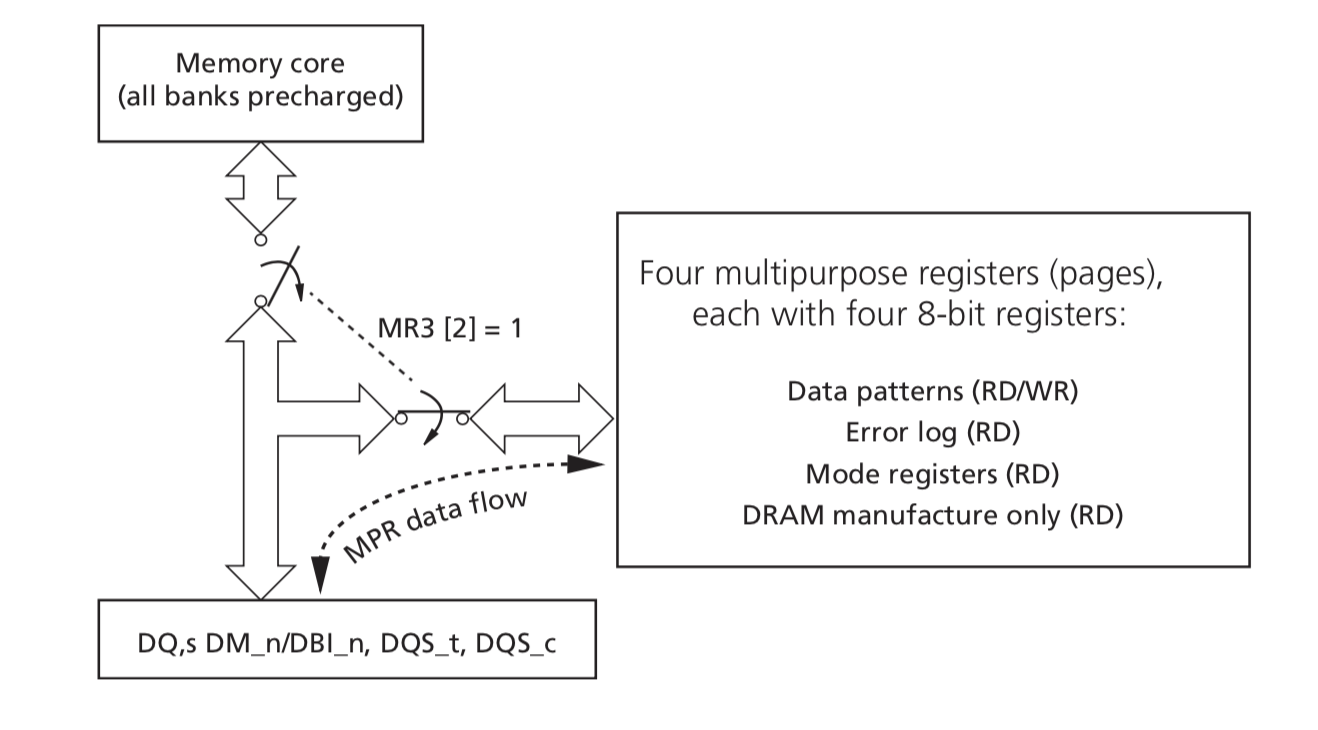

MPR(Multi Purpose Register) Pattern Write는 정확히 말하면 캘리브레이션 알고리즘은 아닙니다. 보통 Read Centering과 Write Centering 이전에 수행되는 단계입니다.

DDR4 DRAM에는 DQ 비트 트레이닝(즉, Read/Write Centering)에 사용되는 4개의 8비트 프로그래머블 레지스터(MPR 레지스터)가 있습니다. MPR 액세스 모드는 모드 레지스터 MR3[2] = 1로 설정하여 활성화합니다. 이 모드가 활성화되면 DRAM에 발행되는 READ/WRITE는 메모리 뱅크 대신 Multi Purpose Register로 리다이렉트됩니다.

그림 13: MPR 읽기/쓰기 (출처: Micron 데이터시트)

읽기 센터링의 목적은 컨트롤러(또는 PHY) 내부의 읽기 캡처 회로가 데이터 아이의 중심에서 데이터를 캡처하도록 트레이닝하는 것입니다. 메모리 컨트롤러(또는 PHY)는 다음을 수행합니다.

1-0-1-0-...라고 가정해 봅시다.읽기 센터링 단계와 유사하게, 쓰기 센터링의 목적은 각 데이터 비트의 쓰기 지연을 설정하여, DRAM 디바이스에서 쓰기 데이터가 해당 쓰기 스트로브 에지에 대해 중앙에 위치하도록 하는 것입니다.

쓰기 센터링 동안 PHY는 다음의 WRITE-READ-SHIFT-COMPARE 루프를 연속적으로 수행합니다.

이 루프를 통해 PHY는 어떤 쓰기 지연 범위에서 정상 데이터가 읽히는지를 판단할 수 있고, 따라서 쓰기 데이터 아이의 좌/우 에지를 알아낼 수 있습니다. 이 데이터를 사용해 WRITE에 대해 DQ를 DQS에 맞춰 센터링합니다.

네트워크 스위치나 라우터 같은 디바이스에서는 동작 중 전압과 온도가 변화할 수 있습니다. 신호 무결성과 데이터 접근의 신뢰성을 유지하기 위해, 초기화 및 읽기/쓰기 트레이닝 동안 트레이닝했던 일부 파라미터를 다시 실행해야 합니다. 메모리 컨트롤러 및 PHY IP는 일반적으로 다음 두 가지 주기적 캘리브레이션 프로세스를 제공합니다.

Periodic ZQ - ZQ Calibration Short(ZQCS)라고도 합니다. 앞서 설명한 240Ω 저항을 튜닝하기 위해 주기적으로 ZQ 캘리브레이션을 실행하는 데 사용됩니다.Periodic Read Centering - 읽기 지연과 기타 읽기 관련 파라미터를 재계산하기 위한 것주기적 캘리브레이션을 활성화하는 것은 선택 사항입니다. 디바이스가 안정적인 온도 조건에서 배치될 것을 알고 있다면, 초기 ZQ 캘리브레이션과 읽기/쓰기 트레이닝만으로 충분합니다.

일반적으로 메모리 컨트롤러 또는 PHY는 레지스터를 통해 타이머를 설정하고 주기적 캘리브레이션을 활성화할 수 있게 해줍니다. 타이머가 설정되면, 타이머가 만료될 때마다 주기적 캘리브레이션이 실행됩니다.

DRAM을 사용하기 전에 완료되어야 하는 단계는 4가지입니다.

이 작업이 끝나면 시스템은 공식적으로 IDLE 상태이며 동작 가능합니다. 디바이스가 배치되는 조건에 따라 주기적 캘리브레이션을 활성화해야 할 수도 있습니다.

이 글에 대한 질문이나 댓글은 아래 링크를 사용해 주세요.

매달 한 번 정도 주목할 만한 기술 논문, 새 글 알림, 그리고 제 경험에서 얻은 교훈을 담은 뉴스레터를 보냅니다.

이 콘텐츠가 유용했다면 이 사이트를 후원해 주시는 것도 고려해 주세요!

Copyright © 2015-2024 Subramani Ganesh